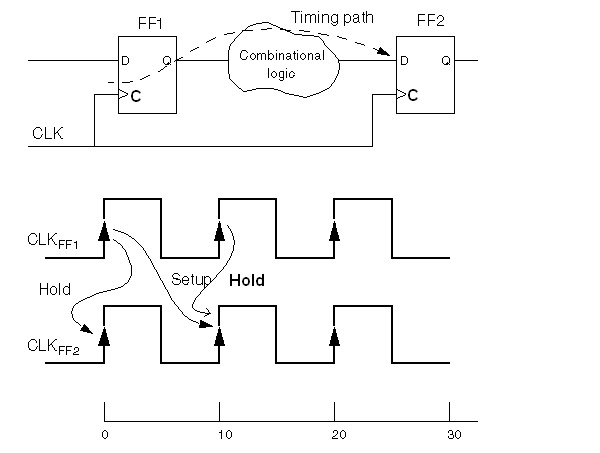

From the Fig its clear that if Slack= Required Time - Arrival time violation at FF2. Hold Check timing can be more clear with the help of following circuit and explanation. 1) If you increase Clock Skew, probability of Hold violation Increase. 2) If you increase Clock Skew, your System output become slow (Means it will take more time to output the data). Please refer.

This timing scenario is called clock used as data.This topology is usually not recommended as timing closure on such paths can be tricky.What is most likely happening in this case is that the router starts by routing the clock nets, including the segments ending to non-clock pins, and does not revisit these routes later on, even to fix timing violation.Because the LUT5 is placed directly in front of FD/D, the net between LUT/O and FD/D cannot be detoured to fix hold.Hold cannot be fixed with this placement.If the LUT is placed in a different slice, it should be ok.